NANDフラッシュで多値記憶が初めて本格化

本連載の第1回では「フラッシュストレージ」が、フラッシュメモリを記憶媒体とするストレージ(データを保存しておくモジュールや装置など)を意味することと、代表的なフラッシュストレージ製品の事例をご説明しました。

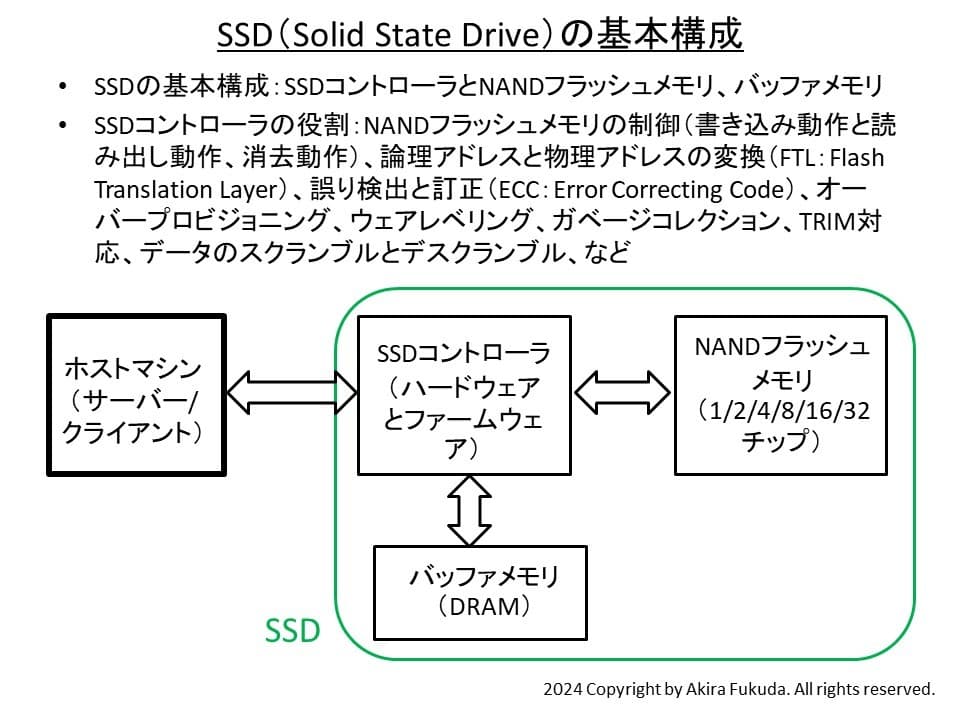

本連載の第2回では、フラッシュメモリにはNANDタイプとNORタイプがあり、ストレージに使われるのはNANDタイプのフラッシュメモリ(「NANDフラッシュメモリ」あるいは「NANDフラッシュ」とも呼ばれる)であること、代表的なフラッシュストレージであるSSD(Solid State Drive)の内部ブロックとSSDコントローラの役割について概略を述べました。

本連載の第3回では、もう1つの代表的なストレージであるハードディスク装置(HDD:Hard Disk Drive)と、SSDの共通点と相違点を簡単に述べるとともに、SSDが特有の複雑さを抱えている原因と対処手法を簡単に記述しました。

第4回となる今回は、SSDコントローラが扱わなければならない特有の記憶技術「多値記憶」の概要と利害得失をまず説明します。次に、多値記憶を採用したNANDフラッシュメモリをSSDでコントローラがどのように扱っているかを解説します。

「多値記憶」技術とは何か

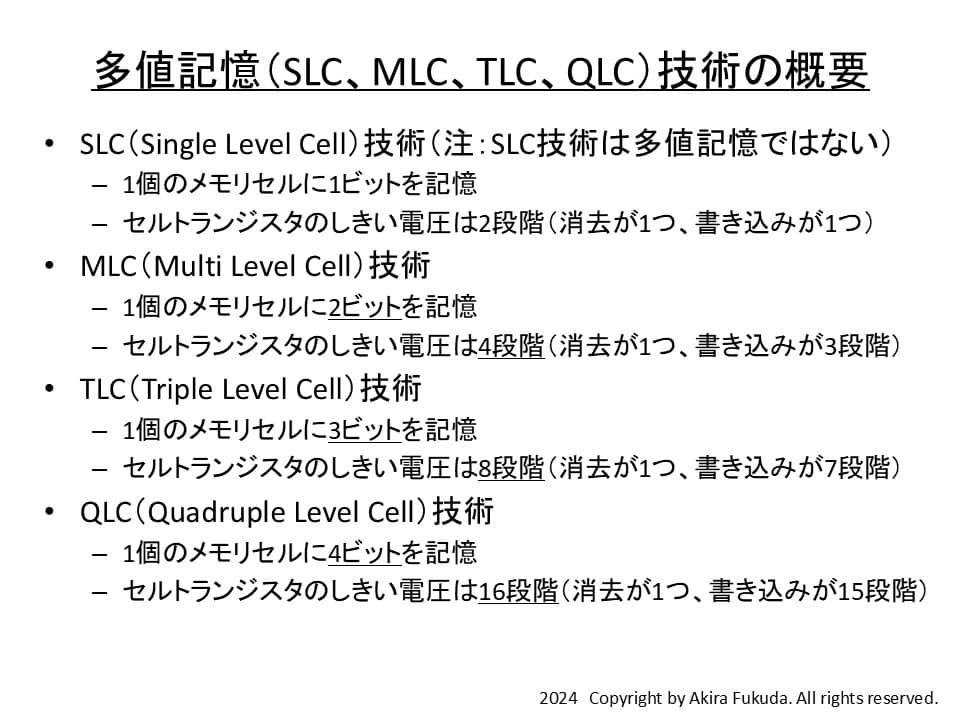

多値記憶とは、1個のメモリセルに2ビット以上のデータを記憶させることです。別の表現をすると、普通の半導体メモリは1個のメモリセルに1ビットのデータを記憶させています。論理値で表現すると「1」あるいは「高レベル」と、「0」あるいは「低レベル」となります。物理的には、トランジスタのしきい電圧(高低)であったり、キャパシタが保持する電荷量(大小)であったり、抵抗素子の抵抗値(高低)であったりします。

ここで物理量の高低や大小などが2通りではなく、4通りあれば、2ビットのデータを記憶できます。といっても実際に4通りの物理量を保持することは簡単ではありません。隣接する論理値との境界(マージン)が狭くなるので、不良が発生しやすくなるからです。研究開発レベルでは試作例が数多くあるものの、商業化できたのはフラッシュメモリが初めてです。

フラッシュメモリ(以降はNANDフラッシュと表記)の場合はトランジスタ(セルトランジスタ)のしきい電圧がデータの値となります。例えば2ビットの多値記憶では、4通りのしきい電圧をトランジスタに書き込み、保持しています。厳密には消去(イレーズ)動作で書き込むしきい電圧が最も低く、プログラム動作で書き込むしきい電圧が3通りある(消去時に比べて高いしきい電圧)ということになります。

3D NANDフラッシュの多値記憶

NANDフラッシュは、3次元化した3D NANDフラッシュを開発して実用化したことで、1個のメモリセル(セルトランジスタ)が記憶するビット数を増やせるようになりました。NANDフラッシュのしきい電圧はセルトランジスタのゲート(あるいはゲート絶縁膜)が保持する電荷の量によって変わります。3次元化によってセルが蓄えられる電荷量が増加(プレーナーNANDフラッシュの約3倍とされています)したことで、従来のNANDフラッシュ(プレーナーNANDフラッシュ)と比べてセルトランジスタのしきい電圧をきめ細かに調整できるようになりました。その結果、1個のメモリセルが記憶可能なビット数が増えたのです。

3D NANDフラッシュでは主に、1個のメモリセルに3ビットを記憶するTLC(Triple Level Cell)技術と、1個のメモリセルに4ビットを記憶するQLC(Quadruple Level Cell)技術が実用化されています。

従来のNANDフラッシュ(プレーナー NANDフラッシュ)では主に、1個メモリセルに2ビットを記憶するMLC(Multi Level Cell)技術が実用化されています。もちろん、1個のメモリセルに1ビットを記憶する従来方式のNANDフラッシュも市販されています。なお1個のメモリセルに1ビットを記憶する場合は多値記憶と区別するため、現在は「SLC(Single Level Cell)」と呼んでいます。

記憶の多値化によるトレードオフ

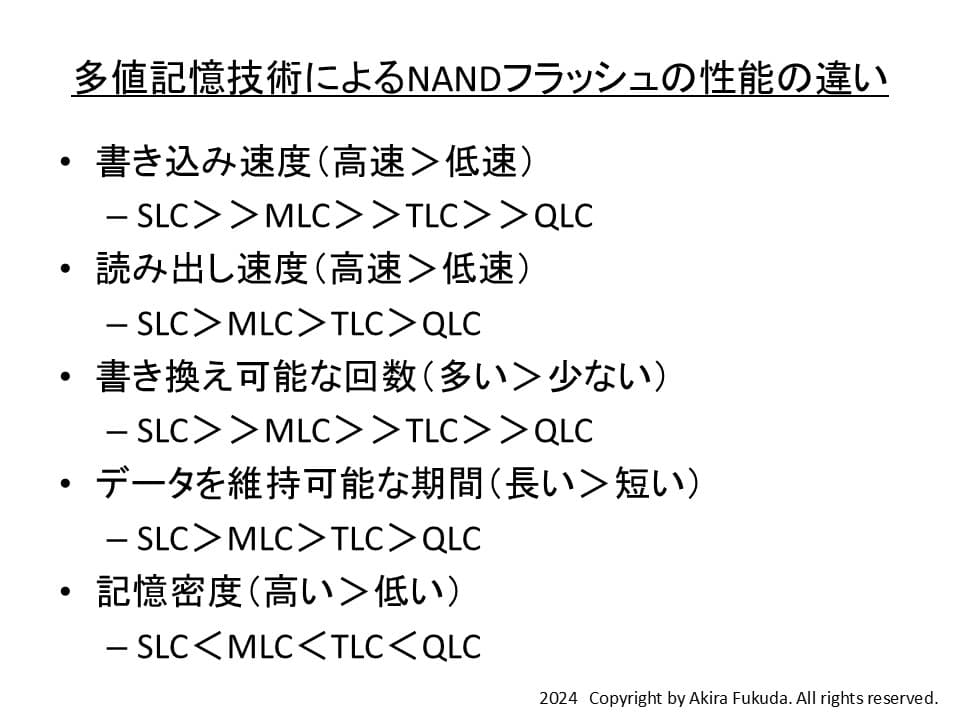

多値記憶の長所は言うまでもなく、記憶密度が向上することです。物理的には1ビットのメモリセルでも、多値記憶技術によって3ビット、さらには4ビットのデータを記憶できるようになります。原理的には記憶密度が3倍、さらには4倍に向上します。

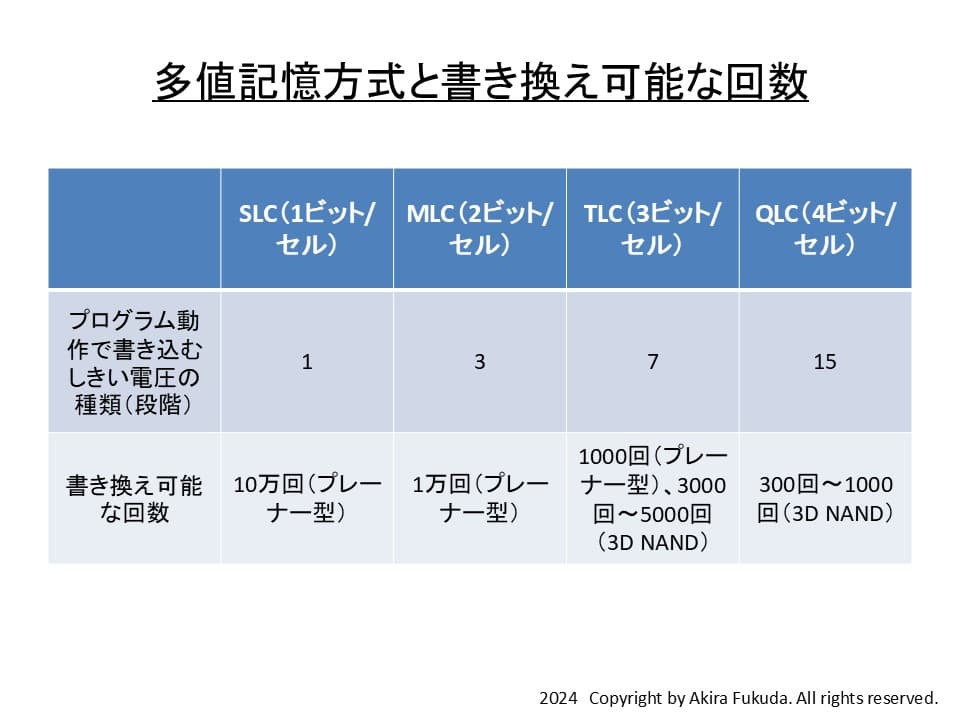

しかし多値化によって生じる短所は少なくありません。まず、データを書き換え可能な回数(「エンデュランス」または「書き換え寿命」)が減少することです。隣接するしきい電圧間の電圧余裕(マージン)が減り、書き換えの繰り返しによる劣化が同じでも、SLC技術よりも早く不良が顕在化するからです。

SLC技術ではおおむね10万回(プレーナーNANDフラッシュの場合)の書き換え寿命があります。TLC技術ですと書き換え寿命は3000回~5000回(3D NANDフラッシュの場合)に下がり、QLC技術に至っては300回から1000回(3D NANDフラッシュの場合)とされています。SLCとQLCを比べると、書き換えが可能な回数は100分の1以下と短くなってしまうのです。

もう1つの短所は、データの書き換えに時間がかかることです。前回で述べたように、NANDフラッシュでは消去済みのブロックに対してデータを書き込みます。具体的にはセルトランジスタのしきい電圧を変更しています。TLC技術ですと7段階、QLC技術だと15段階のしきい電圧があります。フラッシュストレージの外部からは1回のデータ書き込みに見えても、内部では2回~3回に分けてしきい電圧を細かく調整することになります。

SSDの場合、この調整作業はSSDコントローラが担当しています。SSDコントローラは多値記憶のNANDフラッシュに対し、しきい電圧の調整や検証などを含めた「真のプログラム回数」を把握しなければなりません。

さらに、データの読み出しにも時間がかかるほか、データを保持しておける期間(「データリテンション」または「データ保持期間」)が短くなるという弱点があります。これらの性能は1個のメモリセルに記憶させるビット数が増加すると、加速度的に悪化します。

多値記憶の弱点を緩和するSLCバッファ技術

3D NANDフラッシュで実用化されている多値記憶技術の中で、最も高度なのはQLC方式(4ビット/セル方式)です。研究開発レベルでは1個のメモリセルに5ビットを記憶するPLC(Penta-Level Cell)方式の大容量3D NANDフラッシュが発表されています。ただし今のところ(2024年8月末時点)、PLC方式が実用化されるとの公式発表はありません。

TLC方式(3ビット/セル方式)とQLC方式(4ビット/セル方式)のNANDフラッシュでは、SSDにおける使い分けがかなり明確です。データの読み書きが高速なSSDにはTLC方式のNANDフラッシュ、データの記憶容量が大きなSSDにはQLC方式のNANDフラッシュを採用していることが一般的だと言えます。

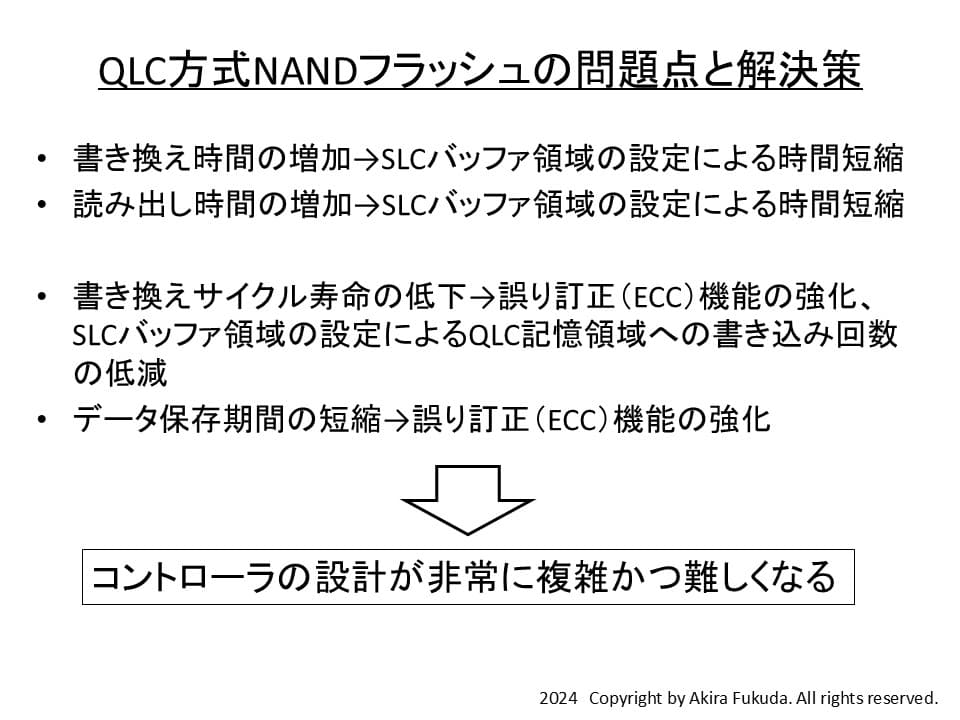

QLC方式のNANDフラッシュを搭載したSSDだからと言って、データの書き込みや読み出しなどに時間がかかり過ぎるのも実用的には問題となります。そこで一部のQLC方式NANDフラッシュ搭載SSDでは、記憶可能な領域の一部をSLC方式で読み書きすることで動作速度を高めています。SLC方式の領域を「SLCバッファ」と呼びます。SLCバッファの効果は非常に大きく、QLC方式NANDフラッシュ搭載のSSD製品がSLCバッファの導入により、TLC方式SSD製品(SLCバッファなし)を超える性能を備えることすらあります。

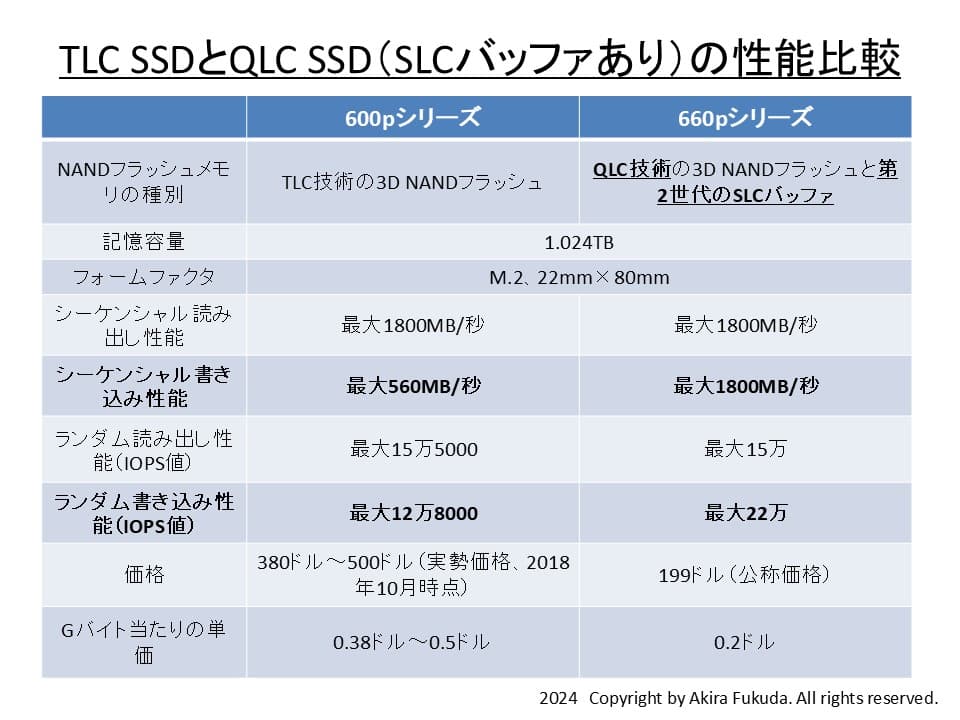

少し古い製品ですが、Intelが製品化したTLC方式NANDフラッシュ搭載SSD(TLC SSD)「600pシリーズ」とSLCバッファを導入したQLC方式NANDフラッシュ搭載SSD(SLCバッファ付きQLC SSD)「660pシリーズ」では、後者の書き込み性能が前者を大きく上回っています。

ユーザーデータの大小に応じてSLCバッファの容量を調整

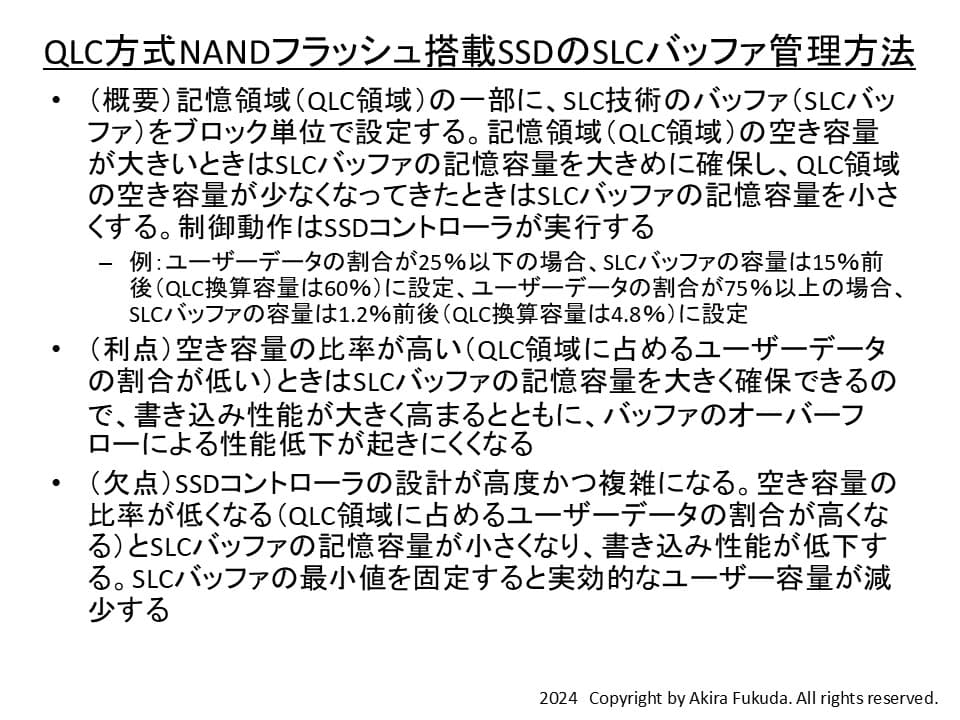

QLC方式のNANDフラッシュを搭載したSSDにおける「SLCバッファ」領域の記憶容量は通常、固定されていません。ユーザーデータがSSDの記憶可能な容量に占める割合に応じて「SLCバッファ」の容量を調整しています。簡単に言えば、ユーザーデータが少ないときにはSLCバッファを大きく確保し、ユーザーデータが多いときにはSLCバッファの容量を少なくしています。

例えばユーザーデータの比率が25%以下のときは、SLCバッファの容量を全体の15%前後と最大化します(最大記憶容量1TバイトのSSDの場合は、SLCバッファ領域が140Gバイトとなります)。15%は少なめに見えますが、QLC換算の容量では全体の40%~60%です。ユーザーデータを25%と仮定して合計すると65%~85%となり、全体ではかなりの領域を占めていることが分かります。

逆にユーザーデータの比率が75%を超えるときは、SLCバッファの容量を全体の1.2%前後と最小化します(最大記憶容量1TバイトのSSDの場合は、SLCバッファ領域が12Gバイトとなります)。QLC換算の容量では全体の4.8%です。ユーザーデータを75%と仮定すると合計で79.8%となります。ここで問題となるのはSLCバッファの最小値を1.2%前後に固定してゼロにしない場合、実効的なユーザー容量が5%ほど減ることです。

SLCバッファ領域の調整と管理はSSDコントローラ(およびファームウェア)が担います。SSDコントローラの設計がさらに難しくなるという課題もあります。